Двоичный счетчик К155ИЕ5

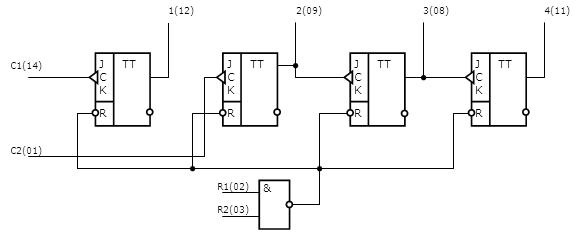

Рис. 4.1 К155ИЕ5

Быстродействующий счетчик К155ИЕ5 представляет собой асинхронный делитель частоты на триггерах типа JK.

Функциональная схема счетчика содержит четыре триггера:

Первый триггер, имеющий тактовый вход С1 и изолированный от других триггеров прямой выход 1, представляет собой счетчик-делитель на два. Три остальных триггера образуют счетчик-делитель на 8. Счетные импульсы при этом должны подаваться на вход С2, а частота, деленная на 8, снимается с выхода 4. Счетчики работают самостоятельно, однако установка их производится одновременно с помощью двух установочных входов R1 и R2, которые обеспечивают два режима работы. Значения сигналов на установочных входах для различных режимов работы счетчиков приведены в таблице 3.

|

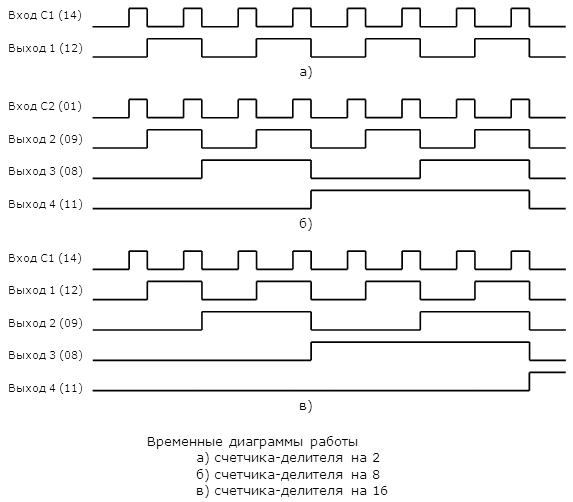

Переключение триггеров происходит по каждому заднему фронту тактовых импульсов:

Путем внешнего соединения выхода 1 со входом С2 образуется двоичный счетчик-делитель на 16:

Рис. 4.4 Двоичный счетчик-делитель на 16

Счетные импульсы при этом подаются на вход С1, а частота, деленная на 16, снимается с выхода 4. В режиме счета состояния выходов триггеров меняются в последовательности двоичного счета от 0 до 15.

Двоично-десятичный четырехразрядный счетчик К155ИЕ2

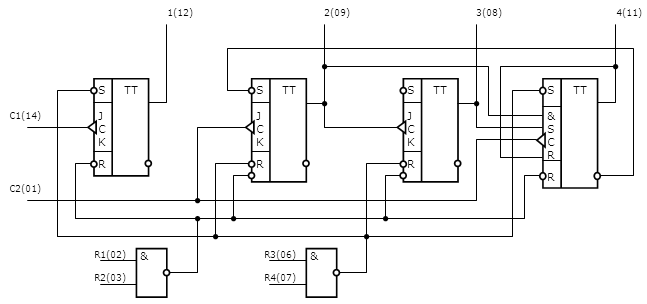

Рис. 2.1 К155ИЕ2

Быстродействующий декадный счетчик представляет собой асинхронный делитель частоты на триггерах типа JK.

Функциональная схема счетчика содержит четыре триггера:

Первый триггер, имеющий тактовый вход С1 и изолированный от других триггеров прямой выход 1, представляет собой счетчик-делитель на два. Три остальных триггера образуют счетчик-делитель на 5. Счетные импульсы при этом должны подаваться на вход С2, частота, деленная на 5, снимается с выхода 4.

Счетчики работают самостоятельно, однако установка их производится одновременно с помощью четырех установочных входов R1-R4, которые обеспечивают три режима работы счетчиков.

Значения сигналов на установочных входах для различных режимов работы счетчиков приведены в таблице 1.

|

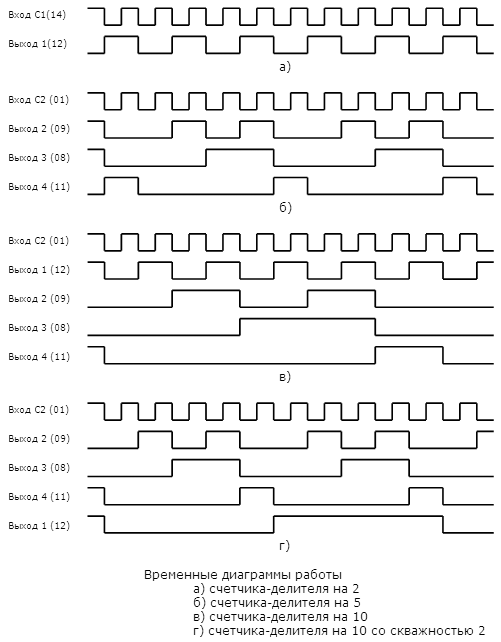

Переключение триггеров происходит по каждому заднему фронту входных тактовых сигналов:

Путем внешнего соединения выхода 1 со входом С2 образуется двоично-десятичный счетчик-делитель на 10. Счетные импульсы при этом подаются на вход С1, а частота, деленная на 10, снимается с выхода 4. В режиме счета состояния выходов триггеров меняются в последовательности двоично-десятичного счета.

Путем внешнего соединения выхода 4 со входом С1 образуется счетчик-делитель на 10 со скважностью, равной 2.Счетные импульсы при этом должны подаваться на вход С2, а частота, деленная на 10, снимается с выхода 1:

Рис. 2.4 Двоично-десятичный счетчик-делитель на 10

Рис

2.5 Cчетчик-делитель на 10 со скважностью, равной 2

В режиме счета состояния выходов триггеров меняются в последовательности двоичного счета от 0 до 4 и далее от 8 до 12.

2.4. Требования к устойчивости при климатических воздействиях

2.4.1. Микросхемы должны быть устойчивыми к воздействию климатических факторов:

сухое тепло:

верхнее значение 343 К (70 °С);

холод:

нижнее значение 263 К (-10 °С);

смена температур от 263 до 343 К (от -10 до +70 °С);

влажное тепло (постоянный режим с относительной влажностью без конденсации влаги) % при 313 ± 2 К (40 ± 2 °С)

Таблица 2

|

Наименование параметра и режим измерения |

Буквенное обозначение параметра |

Норма |

Температура, К (°С) |

||

|

не менее |

не более |

||||

|

Выходное напряжение низкого уровня, В: |

От 263 до 343 (от -10 до +70) |

||||

|

К155ЛА2 К155ЛА3 |

UСС= 5В ± 5 %; UIL = 0,8,В (К155ТМ2); |

UOL |

0,4 |

||

|

К156ТМ2 |

UIH = 2,0 В; UOL = 16 мА |

||||

|

Выходное напряжение высокого уровня, В: |

|||||

|

К155ЛА2 К155ЛА3 К155ТМ2 |

UСС = 5 В ± 5 %; UIL = 0,8 В; UI = 4,75 В; Iон= —0,4 мА; UIH = 2,0 В (K155TM2) |

UOH |

2,4 |

||

|

Ток потребления при низком уровне на выходе, мА: |

|||||

|

К155ЛА2 |

Ucc= 5В ± 5 % |

UCCL |

6 |

||

|

К155ЛА3 |

UI = 5 В |

22 |

|||

|

Ток потребления при высоком уровне на выходе, мА: |

|||||

|

К155ЛА2 |

UCC = 5 B ± 5 %; |

Icch |

2 |

||

|

К155ЛА3 |

UI= 0 В |

8 |

|||

|

Ток потребления, мА: |

От 263 до 343 (от -10 до +70) |

||||

|

К155ТМ2 |

Ucc = 5 B ± 5 % UI= 0 В; 5 В |

IСС |

30 |

||

|

Входной ток низкого уровня, мА: |

IIL |

||||

|

К155ЛА2 К155ЛА3 |

UCC = 5 B ± 5 %; UIH= 4,5В; UIL = 0,4 В; UСс = 5 В ± 5 %; |

-1,6 -1,6 |

|||

|

К155ТМ2 |

UIH = 4,5 В; UIL1 = 0 В; UIL2 = 0,4 В |

-1,6 (по входам 10, 12, 2, 4) -3,2 (по входам 13, 11, 1, 3) |

|||

|

Входной ток высокого уровня, мА: |

|||||

|

К155ЛА2 К155ЛA3 |

UCC = 5 В ± 5 %; UIH= 2,4В; UIL= 0 B |

IIH |

0,04 |

||

|

Входной ток высокого уровня, мА: |

IIH |

||||

|

К155ТМ2 |

Uсс= 5 В ± 5 %; UIH1 = 4,5 В; UIH2 = 2,4 В; UIL = 0 В |

0,04 (по входам 12, 2) 0,08 (по входам 10, 11, 4, 3) 0,12 (по входам 13, 1) |

|||

|

Время задержки распространения сигнала при включении, нc |

От 263 до 343 (от -10 до +70) |

||||

|

К155ЛА2 |

Uсс = 5 В ± 5 %; |

tPHL |

15 |

||

|

К155ЛА3 |

С∑H = 15 пФ ± 15 %; |

15 |

|||

|

К155ТМ2 |

RH = 390 Ом ± 15 %; UIH= 2,4 B |

40 |

|||

|

Время задержки распространения сигнала при выключении, нc |

|||||

|

К155ЛА2 |

UСС = 5 В ± 5 %; |

tPLH |

22 |

||

|

К155ЛА3 |

С∑H =15 пФ ± 15 %; |

22 |

|||

|

К155ТМ2 |

RH = 390 Ом ± 5 %; |

25 |

|||

|

UIH = 2,4 В |

Примечание. Знак «-» перед значениями норм токов IIL,IOS или токов, задаваемых в виде режимных при измерении параметров UD,UОН(см. табл. , , — ), означает направление тока, вытекающего из вывода микросхемы.

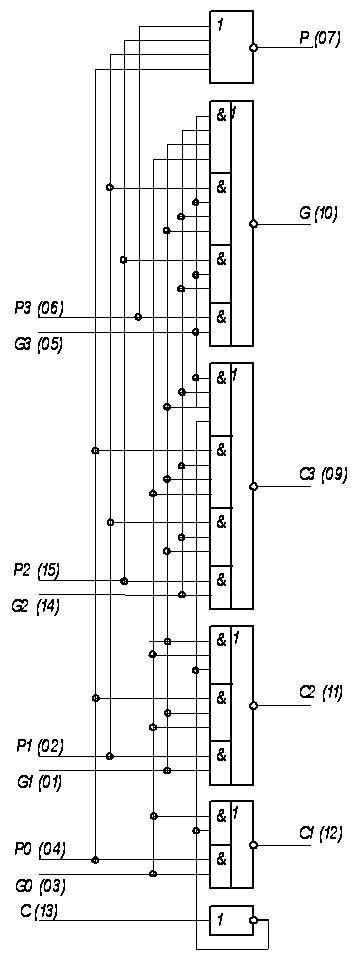

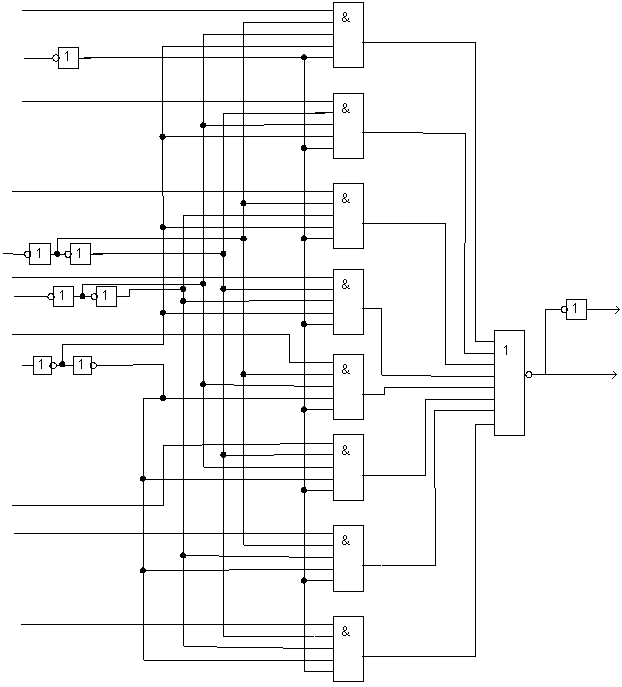

Блок ускоренного переноса для АЛУ К155ИП4

Рис. 12.1 К155ИП4

Схема К155ИП4 представляет собой быстродействующий блок ускоренного переноса, предназначенный для формирования сквозного переноса через четыре каскада при выполнении операции сложения в параллельном сумматоре и используется в сочетании с АЛУ К155ИП3.

Блок содержит четыре входа Р0-Р3, на которые подаются сигналы распространения переноса G0-G3 для сигналов образования переноса, вход переноса из предыдущего разряда С, используемый при каскадировании схем, а также выходы С1, С2, С3 для формирования переносов соответственно с первого, второго и третьего разрядов. С целью расширения логических возможностей схемы сигнал переноса четвертого разряда делится на сигнал образования группового переноса G и сигнал распространения переноса P.

С помощью данной микросхемы можно организовать сквозной перенос между между группой в пределах 16 разрядов, а с применением каскадирования — сквозной перенос в 32 и более разрядных устройствах, построенных по принципу последовательного переноса.

Если ускоренный перенос осуществляется более чем на 4 двоичных разряда, выходы G и P группового переноса АЛУ соединяются со входами блока К155ИП4 на следующем уровне ускоренного переноса.

Асинхронные счётчики

Данные типы счётчиков состоят из цепочёк JK-триггеров, которые работают в счётном режиме, когда выход предыдущего триггера служит входом для следующего. В такой схеме триггеры включаются последовательно, а, следовательно, и выходы счётчика также переключаются последовательно, один за другим (отсюда второе название асинхронных счётчиков – последовательные счётчики). Так как переключение разрядов происходит с некоторой задержкой, поэтому и сигналы на выходах счётчика появляются не одновременно с входным сигналом и между собой, то есть асинхронно.

Микросхемы асинхронных счётчиков применяются не очень часто, в качестве примера можно привести микросхемы типа ИЕ2 (четырёхразрядный двоично-десятичный счётчик), ИЕ5 (четырёх разрядный двоичный счётчик) и ИЕ19 (сдвоенный четырёхразрядный счётчик).

Асинхронные счётчики: слева направо ИЕ2, ИЕ5, ИЕ19.

Данные типы счётчиков имеют входы сброса в нуль (вход R), вход установки в 9 (вход S у ИЕ2), счётный или тактовый вход (вход С) и выходы, которые могут обозначаться как номера разрядов (0, 1, 2, 4) или как вес каждого разряда (1, 2, 4, 8).

Микросхема К555ИЕ2 относится к двоично-десятичным счётчикам, то есть счёт у неё идет от 1 до 9, а потом выводы обнуляются и счёт идёт сначала. Внутренне данный счётчик состоит из четырёх триггеров, которые разделены на две группы: один триггер (вход С1, выход 1) и три триггера (вход С2, выходы 2, 4, 8). Такая внутренняя организация позволяет значительно расширить применение данного типа микросхемы, например данную микросхему можно использовать в качестве делителя на 2, на 5 или на 10. Счётчик ИЕ2 имеет два входа для сброса в нуль объединенных по И, а так же два входа для установки в 9 тоже объединённых по И.

Для реализации счёта необходимо сбросить счётчик подачей на входы R высокого логического уровня, а на один из входов S сигнал низкого уровня. В таком режиме счётчик будет «обнулён» и последовательный счёт заблокирован. Чтобы восстановить функцию счета необходимо установить на входы R низкий уровень сигнала.

Для организации делителя на 2 необходимо подавать сигнал на С1, а снимать с выхода 1; делитель на 5 подавать сигнал на С2, а снимать с выхода 8; делитель на 10 выход 8 соединяют с С1, сигнал подают на С2, а снимают с выхода 1.

Микросхема К555ИЕ5 представляет собой двоичный счётчик, в отличие от ИЕ2 считает до 16 и сбрасывается в нуль. Также как и ИЕ2 состоит из двух групп триггеров со входами С1 и С2, а выходы 1 и 2,4,8. В отличии от ИЕ2 имеет только два входа сброса в нуль, а входов установки нет.

Микросхема К555ИЕ19 практически идентична двум микросхемам К555ИЕ5 и представляет собой два чётырёхразрядных двоичных счётчика, каждый счётчик имеет свой счётный вход С и вход сброса R. Если объединить выход 8 первого счётчика и вход С второго счётчика, то можно получить восьмиразрядный двоичный счётчик.

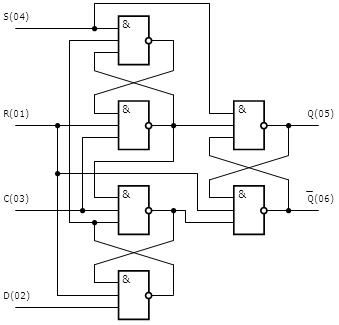

2 D-триггера К155ТМ2

Рис. 26.1 К155ТM2

Микросхема содержит два независимых D-триггера, имеющих общую цепь питания. У каждого триггера есть входы D, S# и R#, а также комплементарные выходы Q и Q#. Входы S# и R# — асинхронные, потому что они работают (сбрасывают состояния триггера) независимо от сигнала на тактовом входе; активный уровень для них – низкий. Сигнал от входа D передается на выходы Q и Q# по положительному перепаду импульса на тактовом входе С (Н → В).

Чтобы триггер переключался правильно, уровень на входе D следует зафиксировать заранее, перед приходом тактового сигнала. Защитный интервал должен превышать время задержки распространения сигнала в триггере. Если на входы S# и R# триггеров одновременно подаются напряжения низкого уровня, состояние выходов Q и Q# окажется неопределенным. Загрузить в триггер входные уровни В или Н ( то есть 1 или 0) можно, если на входы S# и R# подать напряжения высокого уровня.

Асинхронная установка нужного сочетания уровней на выходах получится, когда на входы S# и R# поданы взаимопротивоположные логические сигналы. В это время входы C и D отключены.

|

2.5. Дополнительные требования

2.5.1. Микросхемы должны быть устойчивыми к воздействию следующих факторов:

удара с ускорением 1470 м/с2;

пребывания при температуре 223 К (-50 °С);

пониженного атмосферного давления 660 Па при 298 К (25 °С);

повышенного атмосферного давления 297200 Па.

Таблица 3

|

Тип микросхемы |

Наименование параметра и режим измерения |

Буквенное обозначение параметра |

Норма* |

Температура, К (°С) |

|

|

не менее |

не более |

||||

|

Ток короткого замыкания, мА: |

От 263 до 343 (от -10 до +70) |

||||

|

К155ЛА2 |

UIL = 0 B; |

Ios |

-18 |

-55 |

|

|

К155ЛА3 К155ТМ2 |

Uсс = 5 В ± 5 % |

||||

|

Напряжение блокировки антизвонных входных диодов, В: |

|||||

|

К155ЛА2 |

Uсс = 5 В ± 5 %; |

Ud |

-1,5 |

||

|

К155ЛА3 |

UIH = 4,75 В; |

||||

|

К155ТМ2 |

ID = -10 мА |

||||

|

Ток входной пробивной, мА |

|||||

|

К155ЛА2 |

Uсс = 5 В ± 5 %; |

Iвх.проб |

1 |

||

|

К155ЛА3 |

UIH = 5,5 В; |

||||

|

K155TM2 |

UIL= В |

* См. примечание к табл. .

Таблица 4

|

Норма |

||

|

не менее |

не более |

|

|

Максимальное выходное напряжение, В |

5,25 |

|

|

Кратковременное максимальное напряжение источника питания, В |

7* |

|

|

Максимальное входное напряжение, В |

5,5 |

|

|

Минимальное входное напряжение (на входе микросхемы), В: |

||

|

в статическом режиме |

-0,8 |

|

|

в динамическом режиме |

-1,5 |

|

|

Максимальная емкость нагрузки, пФ |

200** |

|

|

Максимальная длительность фронта или среза входного импульса, нc |

150 |

|

|

Максимальный входной вытекающий ток, при котором напряжение блокировки антизвонных диодов не менее -1,5 В, мА |

10 |

* Нормы электрических параметров в процессе воздействия данного напряжения питания не регламентируются.

** Нормы динамических параметров не регламентируются.

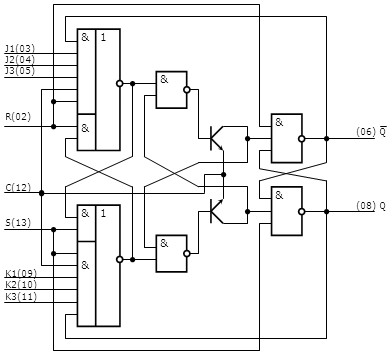

JK-триггер с логикой на входе ЗИ К155ТВ1

Рис. 25.1 К155ТВ1

Микросхема представляет универсальный многоцелевой JK – триггер со структурой “мастер — помощник”. Триггер имеет инверсные входы установки S# и R#. Каждый из входов J и K снабжен трехвходовым логическим элементом И, поэтому у микросхемы три входа J (J1-J3) и три входа К (К1-К3). У триггера имеется тактовый вход C# и комплементарные выходы Q и Q#.

Управление состояниями триггера ТВ1 происходит согласно таблице 12, в которой перечислены 7 режимов его работы. Когда на входах S# и R# присутствуют напряжения высокого уровня, в триггер можно загружать информацию от входов J и K, либо хранить ее. Состояния двухступенчатого триггера переключаются фронтом и срезом положительного тактового импульса: JK-информация загружается в триггер-мастер, когда напряжение тактового входа переходит на высокий уровень и переносится в триггер-помощник по отрицательному перепаду тактового импульса (от В к Н). Отметим, что состояния выходов Q и Q# неопределенные, если на входы S# и R# одновременно поданы напряжения низкого уровня. Кроме того, сигналы на входах J и K не должны меняться, если на входе C# присутствует напряжение высокого уровня.

Входы S# и R# — асинхронные с активным низким уровнем. Когда на эти входы поданы противоположные уровни В и Н, входы С, J и K действовать не будут.

|

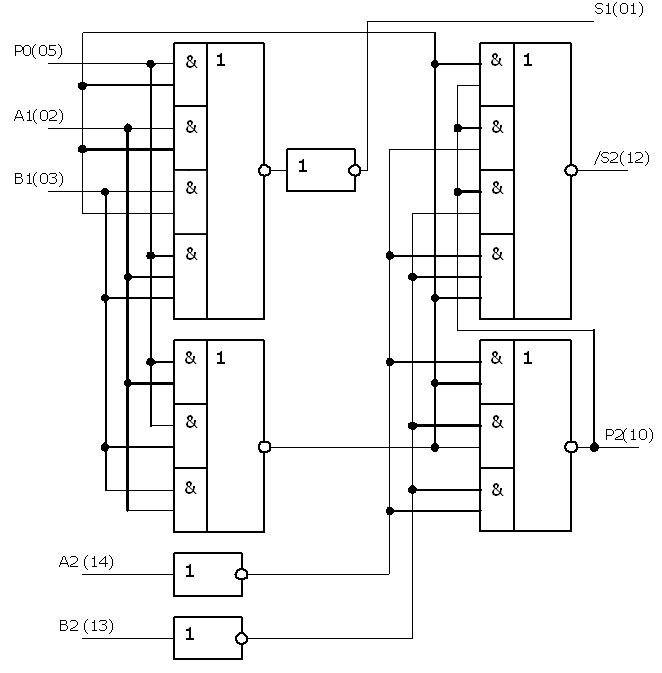

Одноразрядный двоичный сумматор К155ИМ2

Рис. 9.1 К155ИМ2

Сумматор 2-разрядный. Схема имеет по два информационных входа А и В на каждый разряд, вход переноса P0, выходы суммы с первого s1 и второго s2# разрядов и выход переноса со второго разряда P2#.

Схема предназначена для сложения 2-разрядных двоичных чисел. Операция сложения в сумматоре выполняется параллельно, а операция распространения переноса – последовательно.

Наличие инверсии между входом и выходом переноса одного разряда приводит к необходимости в инвертировании входных сигналов второго разряда. Результат суммирования снимается с выхода первого разряда в прямом коде, а с выхода второго разряда – в инверсном коде.

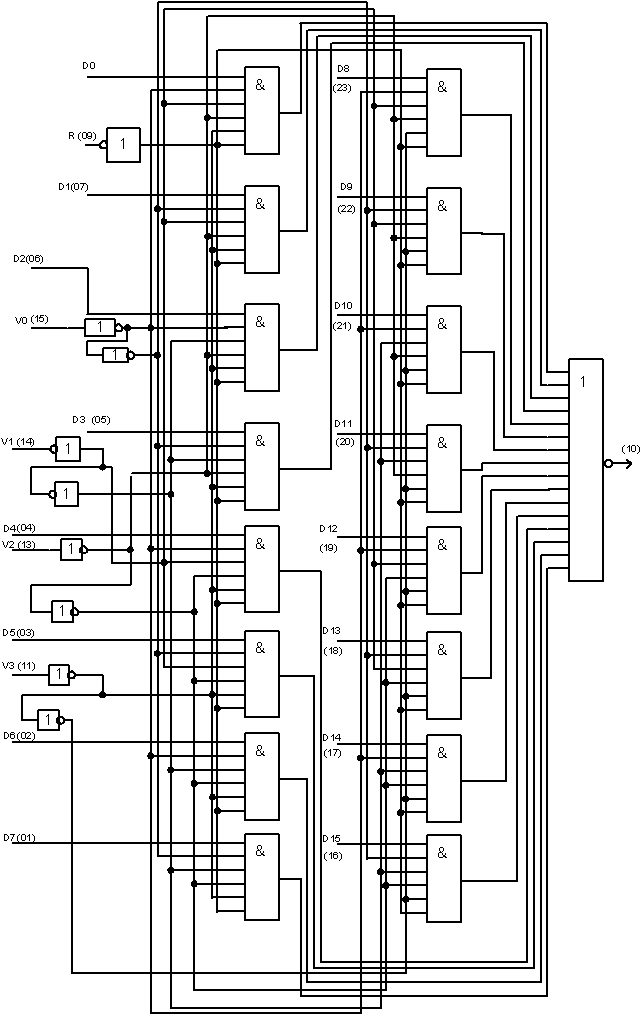

Селектор-мультиплексор на восемь каналов со стробированием К155КП7

Рис. 18.1 К155КП7

Коммутатор восьми входов на один выход со стробированием. t(1→0)=24 нc; t(0→1)=29 нс.

Схема имеет три управляющих входа V0-V2, восемь информационных входов D0-D7, один стробирующий вход R и два выхода.

В зависимости от кодовой комбинации на управляющих входах открывается одна из восьми схем совпадения «И». Сигнал с соответствующего информационного входа будет передан на выход коммутатора как в прямом, так и в инверсном коде. При этом стробирующий вход R должен находиться в состоянии логического нуля. Уровень логической единицы на стробирующем входе запрещает коммутацию любого входа на выход. При этом на выходе (05) будет сохраняться уровень логического нуля.

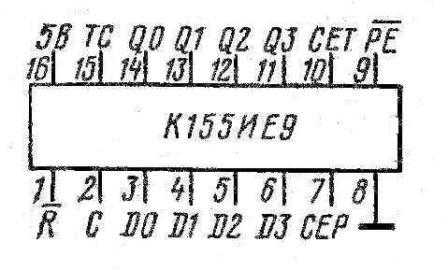

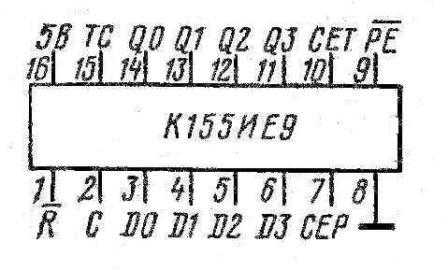

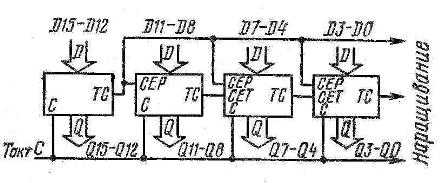

К155ИЕ9 (74160)

|

|

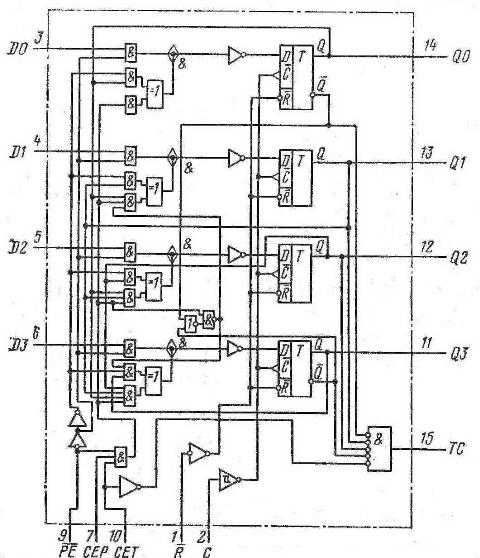

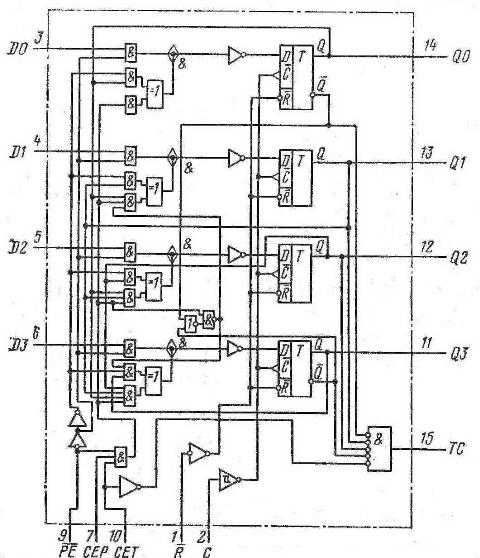

Микросхема К155ИЕ9 (74160) — декадный двоично-десятичный счетчик. Он запускается положительным перепадом тактового импульса и имеет синхронную загрузку (предварительную установку каждого триггера). Несколько счетчиков К155ИЕ9 (74160) образуют синхронный многодекадный счетчик. Сброс всех триггеров асинхронный по общему входу сброса R.

Принципиальная схема высокоскоростного синхронного счетчика отличается внутренней логикой ускоренного переноса и тем, что все триггеры получают перепад тактового импульса одновременно. Изменения выходных состояний триггеров совпадают по времени, поэтому в выходных импульсных последовательностью нет пиковых помех (клыков). Запускающий тактовый фронт импульса — положительный, причем для вариапта этой микросхемы с переходами Шотки буферный элемент тактового входа имеет порог Шмитта с гистерезисом +400мВ , что уменьшает чувствительность к импульсным помехам, а также обеспечивает устойчивое переключение триггеров при медленно нарастающем перепаде тактового импульса.

Счетчик К155ИЕ9 (74160) — полностью программируемый, поскольку на каждом из его выходов можно установить требуемый логический уровень. Такая предварительная установка происходит синхронно с перепадом тактового импульса и не зависит от того, какой уровень присутствует на входах разрешения счета СЕР и CET Напряжение низкого уровня, поступившее на вход параллельной загрузки PE, останавливает счет и разрешает подготовленным на входах D0 — D3 данным загрузиться в счетчик в момент прихода следующего перепада тактового импульса (от низкого уровня к высокому).

Сброс у счетчика К155ИЕ9 (74160) — асинхронный. Если на общий вход сброса R поступило напряжение низкого уровня, на выходах всех четырех триггеров устанавливаются низкие уровни независимо от сигналов на входах С, PE, СЕТ и СЕР. Внутренняя схема ускоренного переноса необходима для синхронизации многодекадной цепи счетчиков К155ИЕ9. Специально для синхронного каскадирования микросхема имеет два входа разрешения: СЕР (параллельный) и CET (вспомогательный, с условным названием «трюковый»), а также выход ТС (окончание счета).

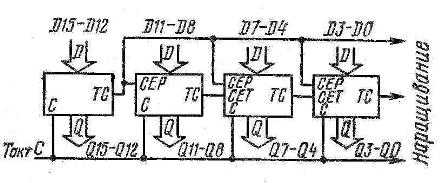

Счетчик считает тактовые импульсы, если на обоих его входах СЕР и СЕТ напряжение высокого уровня. Вход СЕТ последующего счетчика получает разрешение счета в виде напряжения высокого уровня от выхода ТС предыдущего счетчика. Длительность высоких уровней на выходе ТС примерно соответствует длительности высокого уровня на выходе Q0 предыдущего счетчика. На рисунке показана схема соединения четырех микросхем К155ИЕ9 в быстрый синхронный 16-разрядный счетчик.

Для счетчиков К155ИЕ9 (74160) не допускаются перепады от высокого уровня к низкому на входах СЕР и СЕТ, если на тактовом входе присутствует напряжение низкого уровня. Нельзя подавать положительный перепад на вход PE, еели на тактовом входе присутствует напряжение низкого уровня, а на входах СЕР и СЕТ — высокого (во время перепада или перед ним). Сигналы на входах СЕР и СЕТ можно изменять, если на тактовом входе С присутствует напряжение низкого уровня. Когда на входе PE появляется высокий уровень, а входы СЕ не активны (т, е. не используем СЕР и СЕТ и на них остается низкий уровень), то вместе с последующим положительным перепадом тактового импульса на выходах Q0 — Q3 появится код от входов D0 — D3.

Запуская напряжениями высокого уровня входы СЕТ и СЕР во время низкоуровневой части такового периода, получим на выходах наложение кодов загрузки и внутреннего счета. Если во время низкоуровневой части периода тактовой последовательности на входы СЕТ, СЕР и PE поданы положительные перепады, нарастающие от низкого уровня к высокому, тактовый перепад изменит код на выходах Q0 — Q3 на последующий.

При входных сигналах высокого уровня счетчик К155ИЕ9 (74160) потребляет ток питания 94 мА, К555ИЕ9 (74 LS169A) 32 мА; если все выходные сигналы имеют низкий уровень, то 101 и 32 мА соответственно. Максимальная частота счета 25 МГц. Время распространения сигнала от входа С до выхода ТС («Счет закончен») составляет 35 и 27 нс, а время сброса (от входа R до выходов Q) 38 и 28 нс для обычного исполнения и варианта Шотки.

Режим работы счетчика К155ИЕ9 (74160) можно выбрать согласно таблице. На выходе ТС появится напряжение высокого уровня, если выходной код счетчика ВННВ (т. е. 9), а на входе CET напряжение высокого уровня.

Режим работы счётчика К155ИЕ9

Режим

Вход

Выход

R

C

СЕР

CET

PE

Dn

Qn

TC

Сброс

Н

х

х

х

х

х

Н

Н

Параллельнаязагрузка

В

↑

х

х

Н

Н

Н

Н

В

↑

х

х

Н

В

В

В

Счет

В

↑

В

В

В

х

Счет

В

Хранение

В

х

Н

х

В

х

qn

В

В

х

х

Н

В

х

qn

В

Зарубежным аналогом счётчика К155ИЕ9 является микросхема .

Селектор-мультиплексор данных на 16 каналов со стробированием К155КП1

Рис. 15.1 К155КП1

Коммутатор (мультиплексор) 16 входов на один выход со стробированием. t(1→0)=15 нc; t(0→1)=22 нс.

Схема имеет 4 управляющих входа V0-V3, 16 информационных входов D0-D15, один стробирующий вход R и один выход.

В зависимости от кодовой комбинации на управляющих входах открывается одна из 16 схем совпадения. Сигнал с соответствующего информационного входа будет передан на выход коммутатора в инверсном коде. При этом стробирующий вход R должен находиться в состоянии логического нуля. Уровень логической единицы на стробирующем входе запрещает коммутацию любого входа на выход, на котором будет сохраняться уровень логической единицы независимо от состояний информационных входов. Схема может использоваться для преобразования параллельного кода в последовательный.

2.1. Требования к конструкции

2.1.1. Размеры микросхемы должны соответствовать СТ СЭВ …* и черт. .

* См. информационное приложение .

Корпус. Основные размеры

.А — длина вывода, обеспечивающая гарантийный зазор между плоскостью основания микросхемы и установочной плоскостью.

. Нумерация выводов показана условно.

. Корпус с теплорастекателем.

. Зона ключа — место для выполнения знака ключа.

2.1.2. Поверхность микросхемы не должна иметь трещин, раковин и других неровностей, нарушающих габаритные размеры, приводящих к потере работоспособности и ухудшающих надежность микросхемы. Покрытие выводов не должно иметь пузырьков и следов коррозии, приводящих к ухудшению обслуживания выводов.

2.1.3. Масса микросхем не должна превышать 1 г.

2.1.4. Микросхемы не имеют внутренних полостей. Требования к герметичности не предъявляются.

2.1.5. Выводы микросхем должны быть механически прочными и выдерживать без повреждений воздействия механических факторов, возникающих при монтаже аппаратуры.

2.1.6. Выводы микросхем должны обеспечивать возможность их пайки при следующих условиях:

минимальной температуре 508 ± 5 К (235 ± 5 °С);

максимальной температуре 543 ± 10 К (270 ± 10 °С);

времени пайки от 2 до 3 с.

2.1.7. Микросхемы должны выдерживать воздействие тепла, возникающего при следующих условиях:

температуре пайки 533 ± 5 К (260 ± 5 °С) при времени лайки не более 8 с;

расстоянии от плоскости основания корпуса до места пайки (по длине выводов) не менее 1,5 мм.

2.1.8. Назначение выводов указано на электрических схемах микросхем*.

* См информационные приложения — .

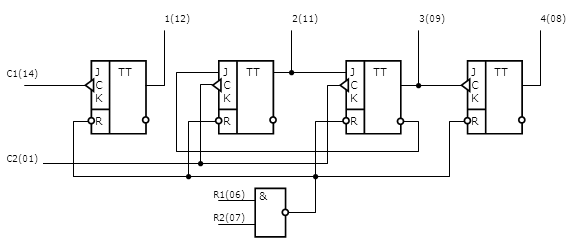

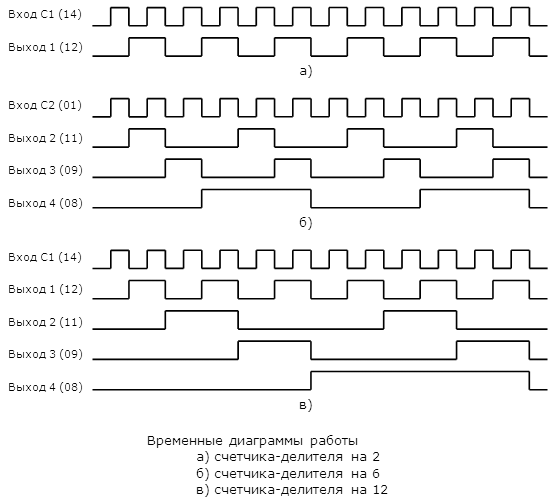

Счетчик-делитель на 12 К155ИЕ4

Рис. 3.1 К155ИЕ4

Быстродействующий счетчик К155ИЕ2 представляет собой асинхронный делитель частоты на триггерах типа JK.

Функциональная схема счетчика включает в своем составе 4 триггера:

Первый триггер, имеющий тактовый вход С1 и изолированный от других триггеров прямой выход 1, представляет собой счетчик-делитель на 2. Три остальных триггера образуют счетчик-делитель на 6.Счетные импульсы при этом должны подаваться на вход С2, а частота, деленная на 6, снимается с выхода 4.

Счетчики работают самостоятельно, однако установка их производится одновременно с помощью двух установочных входов R1 и R2, которые обеспечивают два режима работы. Значения сигналов на установочных входах для различных режимов работы счетчиков приведены в таблице 2.

|

Путем внешнего соединения выхода 1 со входом С2 образуется двоичный счетчик-делитель на 12. Счетные импульсы при этом подаются на вход С1, а частота, деленная на 12, снимается с выхода 4. В режиме счета состояния выходов триггеров меняются в последовательности двоичного счета от 0 до 5 и далее от 8 до 13.

Рис. 3.3 Двоичный счетчик-делитель на 12

Переключение триггеров происходит по каждому заднему фронту входных тактовых импульсов:

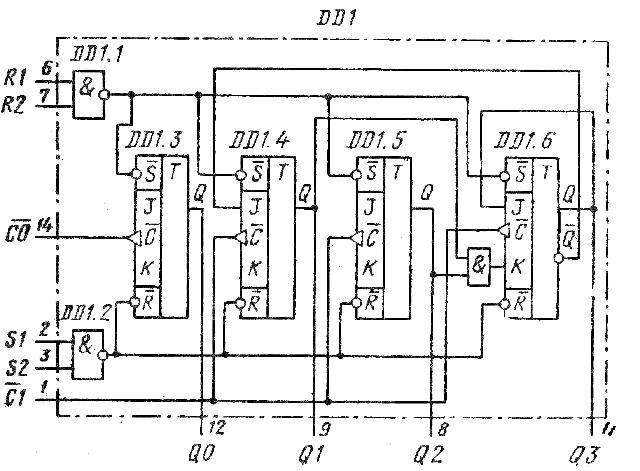

К155ИЕ2 и КМ155ИЕ2 (7490)

|

Микросхемы К155ИЕ2 и КМ155ИЕ2 (7490) четырехразрядный десятичный асинхронный счетчик пульсаций. Внутренняя схема его показана на рисунке. Первый триггер счетчика DD1.3 может работать самостоятельно. Он служит делителем входной частоты в 2 раза, Тактовый вход этого делителя C0 (вывод 14), а выход QO (вывод 12). Остальные три триггера DD1.4 — DD1.6 образуют делитель на 5. Тактовый вход здесь C1 (вывод 1). Для обоих тактовых входов запускающий перепад отрицательный, т. е. от высокого уровня к низкому.

Счетчик имеет два входа R для синхронного сброса (выводы 6 и 7), а также два синхронных входа S (выводы 2 и 3) для предварительной загрузки в счетчик двоичного кода 1001, соответствующего десятичной цифре 9. Поскольку счетчик К155ИЕ2, КМ155ИЕ2 (7490) асинхронный, состояния на его выходах Q0 — Q3 не могут изменяться одновременно. Если -после данного счетчика выходной код, требуется дешифрировать, т. е. перевести его в десятичное число, дешифратор должен стробироватьея на время этой операции. Иначе из-за неодновременности переключения выходных уровней четырех триггеров могут дешифроваться импульсные помехи (клыки).

Входы синхронного сброса RI и R2 (двухвходовой элемент И) запрещают действие импульсов по обоим тактовым входам и входам установки S. Импульс, поданный на вход R, дает сброс данных по всем триггерам одновременно. Подачей напряжения на входы S1 и S2 запрещается прохождение на счетчик тактовых импульсов, а также сигналов от входов R1 и R2. На выходах счетчика Q0 — Q3 (выводы 12, 9, 8, и 11) устанавливаются напряжения выходных уровней ВННВ, что соответствует коду 1001, т. е. цифре 9.

Чтобы получить на выходах счетчика К155ИЕ2, КМ155ИЕ2 (7490) двоично-десятичный код с весом двоичных разрядов 8-4-2-1, необходимо соединить выводы 12 и 1 (т. е. выход Q0 и вход С1. Входная последовательность подается на тактовый вход С0 (вывод 14). Симметричный счетчик-делитель входной частоты в 10 раз получится, если соединить вывод 11 (выход QЗ) с выводом 14 (вход C0). Симметричный способ деления в зарубежной литературе называется bi-quinary, т. е. в переводе — две пятерки. Выходная последовательность при счете двумя пятерками имеет вид симметричного меандра с уменьшенной в 10 раз частотой. Снимается она с выхода Q0 (вывод 12) микросхемы К155ИЕ2 КМ155ИЕ2 (7490).

Для деления частоты на два используется тактовый вход С0 (вывод 14) и выход QО (вывод 12). Для деления частоты в 5 раз подаем входную последовательность на вывод 1. Выходной сигнал получаем на выходе Q3 (вывод 11), Внешние перемычки для этих простых делителей не нужны. Счетчик К155ИЕ2, КМ155ИЕ2 (аналог 7490 ) имеет ток потребления 53 мА и максимальную тактовую частоту 10 МГц. Аналогичная схема варианта 74LS 90 потребляет ток 15 мА и имеет тактовую частоту до 30 МГц.

Режим работы счетчика К155ИЕ2, КМ155ИЕ2 (7490) можно выбрать из таблицы (сброс выходных данных в ноль, установка, т.е. загрузка девятки, счет). В таблице показана последовательность смены напряжений высоких и низких уровней на выходах счетчика К155ИЕ2 и КМ155ИЕ2 (7490) в режиме двоично-десятичного счета, когда требуется соединить внешней перемычкой выход Q0 и вход С1 (т. е. выводы 1 и 12).

Зарубежным аналогом микросхемы КМ155ИЕ2 является микросхема 7490.

| Счет | Выход | |||

| Q0 | Q1 | Q2 | QЗ | |

| В | Н | Н | Н | |

| 1 | В | Н | Н | Н |

| 2 | Н | В | Н | Н |

| 3 | В | В | Н | Н |

| 4 | Н | Н | В | Н |

| 5 | Н | Н | В | Н |

| 6 | Н | В | В | Н |

| 7 | В | В | В | Н |

| 8 | Н | Н | Н | В |

| 9 | В | Н | Н | Н |

R1

R2

S1

S2

Qo

Q1

Q2

Q3

В

В

Н

х

Н

Н

Н

Н

В

В

х

Н

Н

Н

Н

Н

х

х

В

В

В

Н

Н

В

Н

х

Н

х

Счет

х

Н

х

Н

Счёт

Н

х

х

Н

Счёт

х

Н

В

х

Счёт