3.2 Моделирование схемы.

library IEEE;

use IEEE.std_logic_1164.all;

entity Top is

port (

Xi2: in STD_LOGIC_VECTOR (0 to 3);

Yi2: in STD_LOGIC_VECTOR (0 to 3);

Yi3: in STD_LOGIC_VECTOR (0 to 3);

Xi3: in STD_LOGIC_VECTOR (0 to 3);

SIM: in STD_LOGIC;

BB: in STD_LOGIC;

Zpr1: out STD_LOGIC;

Zpr2: out STD_LOGIC;

pd: out STD_LOGIC;

SIP: out STD_LOGIC

);

end Top;

architecture Top_arch of Top is

component k589ap16 is

port (

A: in STD_LOGIC_VECTOR (0 to 3);

B: inout STD_LOGIC_VECTOR (0 to 3);

C: inout STD_LOGIC_VECTOR (0 to 3);

YB: in STD_LOGIC;

BK: in STD_LOGIC

);

end component;

component k155ln1 is

port (

X: in STD_LOGIC;

Y: out STD_LOGIC

);

end component;

component k155id3 is

port (

A: in STD_LOGIC_VECTOR (3 downto 0);

W0: in STD_LOGIC;

W1: in STD_LOGIC;

D: out STD_LOGIC_VECTOR (0 to 15)

);

end component;

component k155id3_1 is

port (

A: in STD_LOGIC_VECTOR (3 downto 0);

W0: in STD_LOGIC;

W1: in STD_LOGIC;

D: out STD_LOGIC_VECTOR (0 to 4)

);

end component;

component k155tl1 is

port (

S: in STD_LOGIC;

T: out STD_LOGIC

);

end component;

component k155id4 is

port (

S1: in STD_LOGIC;

A: in STD_LOGIC;

B: in STD_LOGIC;

D: out STD_LOGIC_VECTOR (1 to 3)

);

end component;

component k155la2 is

port (

V: in STD_LOGIC_VECTOR (0 to 4);

F:out STD_LOGIC

);

end component;

component k155la3 is

port (

X1: in STD_LOGIC;

X2: in STD_LOGIC;

J: out STD_LOGIC

);

end component;

component kp580ik51 is

port (

in1:inout STD_LOGIC_VECTOR (0 to 7);

sbr: in STD_LOGIC;

UD: in STD_LOGIC;

rd: in STD_LOGIC;

wr: in STD_LOGIC;

out1: inout STD_LOGIC;

gpd: inout STD_LOGIC;

gpr: inout STD_LOGIC

);

end component;

component k155ln5 is

port (

H: in STD_LOGIC;

K: out STD_LOGIC

);

end component;

signal zero,n5,n6,n8,n9,n10,n11,n12,n13,n14,n15,n16,n17,n18,n19

: STD_LOGIC;

signal h1 : STD_LOGIC_VECTOR (1 to 3);

signal x1,s1,s11,s2,s22,s3: STD_LOGIC_VECTOR (0 to 3);

signal v1:STD_LOGIC_VECTOR (0 to 15);

signal f1:STD_LOGIC_VECTOR (0 to 4);

signal c1,c2,c3:STD_LOGIC_VECTOR (0 to 3);

signal n1,n:STD_LOGIC_VECTOR (0 to 7);

begin

D5_1:k155ln1

port map (SIM,n5);

D5_2:k155ln1

port map (n5,n6);

D1:k589ap16

port map (Xi2,s1,c1,’0′,’0′);

D2:k589ap16

port map (Yi2,s2,c2 , ‘0’ ,’0′);

D3:k589ap16

port map (Yi3,s3,c3,’0′,’0′);

D4:k589ap16

port map (Xi3,x1,c3,’0′,’0′);

D:k155id3

port map (s3,’0′,’0′,v1);

D_1:k155id3_1

port map (x1,BB,’0′,f1);

D10:k155la2

port map (f1,n8);

D11:k155ln1

port map (n8,n9);

D11_2:k155ln1

port map (n9,n10);

D12_2:k155la3

port map (n10,n10,n11);

D11_3:k155ln1

port map (n11,n12);

D14_4:k155ln5

port map (n12,SIP);

D9:k155id4

port map (n9,x1(1),x1(2),h1);

D12_1:k155la3

port map (h1(1),’1′,n13);

D8:k155tl1

port map (‘0’,n14);

D5_6:k155ln1

port map (n14,n15);

D11_4:k155ln1

port map (x1(3),n16);

D13:kp580ik51

port map

(in1(0)=>s1(0),in1(1)=>s1(1),in1(2)=>s1(2),in1(3)=>s1(3),

in1(4)=>s2(0),in1(5)=>s2(1),in1(6)=>s2(2),in1(7)=>s2(3),

sbr=>n13,UD=>n16,rd=>h1(3),wr=>h1(2),out1=>n17,gpd=>n18,

gpr=>n19);

D14_1:k155ln5

port map (n19,Zpr1);

D14_2:k155ln5

port map (n18,Zpr2);

D14_3:k155ln5

port map (n17,pd);

end Top_arch;

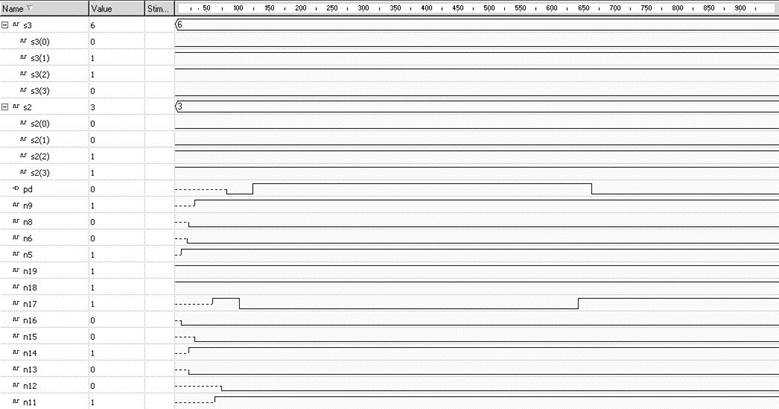

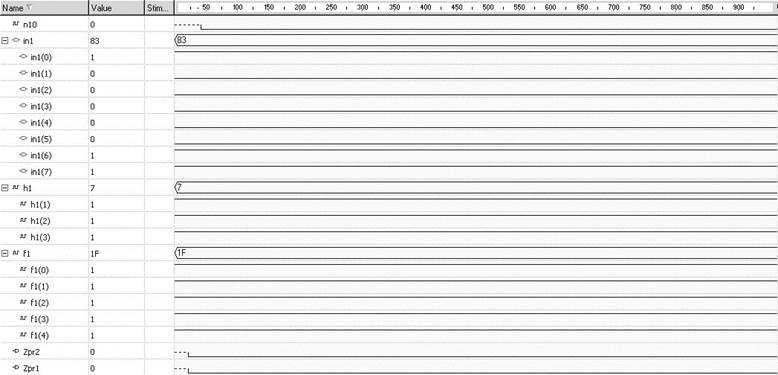

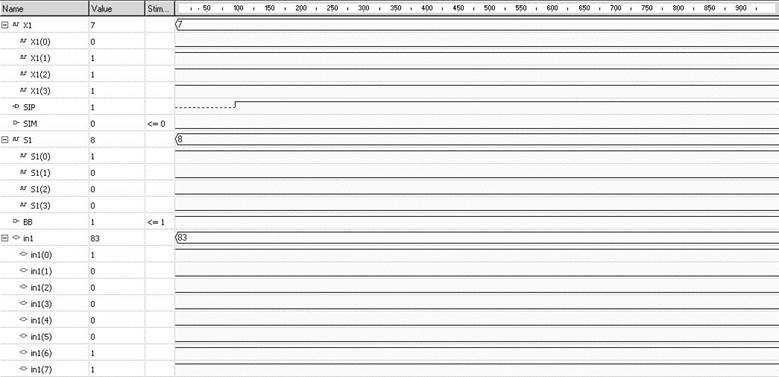

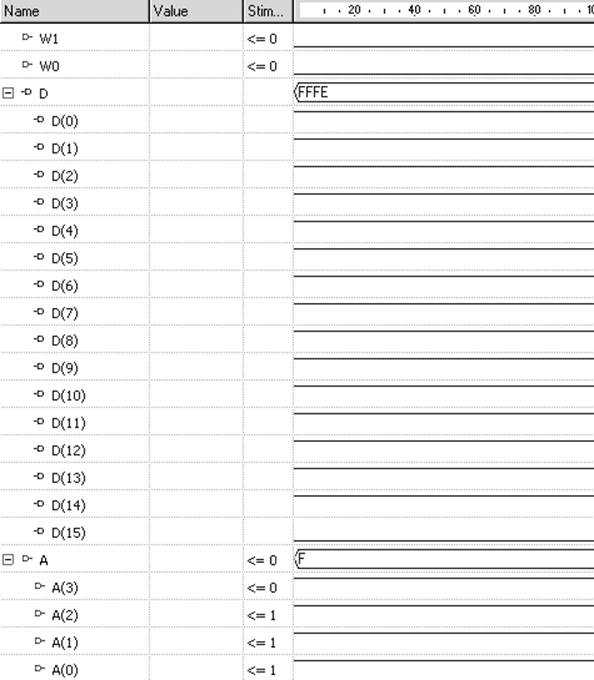

Рис. 16. Временная диаграмма работы схемы приспособления на

базе БИС УСАПП

2.1 Шинный формирователь К589АП16

Микросхема К589АП16 – шинный

формирователь , являющийся параллельным двунаправленным формирователем сигналов

для управления магистралями (шинами) в цифровых вычислительных устройствах и

представляют собой ;-канальные коммутаторы, имеющие в каждом канале одну шину

только для приема информации, одну шину только для выдачи информации и одну

двунаправленную шину для приема и выдачи информации. Рис. 1

Рис. 1 Схема электрическая

принципиальная К589АП16

Таблица 1. Таблица истинности

элемента К589АП16

|

Состояние входов |

Направление передачи |

Выходы в состояние |

|

|

CS |

DCE |

||

|

От входов DI0-DI3 до выходов DB0-DB3 |

DO0-DO3 |

||

|

1 |

От входов DB0-DB3 до выходов DO0-DO3 |

DB0-DB3 |

|

|

1 |

1 |

Передача отсутствует |

DO0-DO3, DB0-DB3 |

В моей схеме имеем 2-ой случай.

Временные диаграммы представлены на рисунке 2.

Рис2

3.1 Моделирование элементов схемы.

Модель элемента К589АП16.

library IEEE;

use IEEE.std_logic_1164.all;

use

IEEE.std_logic_unsigned.all;

entity k589ap16 is

port (

A: in

STD_LOGIC_VECTOR (0 to 3);

B: inout

STD_LOGIC_VECTOR (0 to 3);

C: inout

STD_LOGIC_VECTOR (0 to 3);

YB: in STD_LOGIC;

BK: in STD_LOGIC

);

end k589ap16;

architecture k589ap16 of

k589ap16 is

begin

process(A,B)is

begin

if YB=’0′ and BK=’0′ then

B(0)<=A(0);

B(1)<= A(1);

B(2)<= A(2);

B(3)<= A(3);

elsif YB=’0′ and BK=’1′

then

C(0)<=transport B(0)

after 25 ns;

C(1)<=transport

B(1) after 25 ns;

C(2)<=transport

B(2) after 25 ns;

C(3)<=transport

B(3) after 25 ns;

elsif YB=’1′ and BK=’1′

then

B(0)<=transport ‘0’

after 25 ns;

B(1)<=transport ‘0’

after 25 ns;

B(2)<=transport ‘0’

after 25 ns;

B(3)<=transport ‘0’

after 25 ns;

end if;

end process;

end k589ap16;

Модель элемента К155ЛН1.

library IEEE;

use IEEE.std_logic_1164.all;

entity k155ln1 is

port (

X: in STD_LOGIC;

Y: out STD_LOGIC

);

end k155ln1;

architecture k155ln1 of

k155ln1 is

begin

process (X)is

begin

Y<=transport not X

after 10 ns;

end process;

end k155ln1;

Модель элемента К155ИД3.

architecture k155id3 of

k155id3 is

begin

process (A,W1,W0)is

begin

if A=»0000″ then

D<=»0111111111111111″;

elsif

A=»0001″ then

D<=»1011111111111111″;

elsif

A=»0010″ then

D<=»1101111111111111″;

elsif

A=»0011″ then

D<=»1110111111111111″;

elsif

A=»0100″ then

D<=»1111011111111111″;

elsif A=»0101″ then

D<=»1111101111111111″;

elsif

A=»0110″ then

D<=»1111110111111111″;

elsif

A=»0111″ then

D<=»1111111011111111″;

elsif

A=»1000″ then

D<=»1111111110111111″;

elsif

A=»1010″ then

D<=»1111111111011111″;

elsif

A=»1011″ then

D<=»1111111111101111″;

elsif

A=»1100″ then

D<=»1111111111110111″;

elsif

A=»1101″ then

D<=»1111111111111011″;

elsif

A=»1110″ then

D<=»1111111111111101″;

elsif

A=»1111″ then

D<=»1111111111111110″;

end if;

end process;

end k155id3;

Модель элемента К155ТЛ1.

library IEEE;

use IEEE.std_logic_1164.all;

entity k155tl1 is

port (

S: in STD_LOGIC;

T: out STD_LOGIC

);

end k155tl1;

architecture k155tl1 of

k155tl1 is

begin

process(S)is

begin

T<=transport not S after

22ns;

end process;

end k155tl1;

Модель элемента К155ИД4.

library IEEE;

use IEEE.std_logic_1164.all;

use

IEEE.std_logic_unsigned.all;

entity k155id4 is

port (

S1: in STD_LOGIC;

A: in STD_LOGIC;

B: in STD_LOGIC;

D: out STD_LOGIC_VECTOR

(1 to 3)

);

end k155id4;

architecture k155id4 of

k155id4 is

begin

process(S1,A,B)is

begin

if S1=’1’and A=’0′ and

B=’0’then

D<=»011″;

elsif A=’1′ and B=’0′ then

D<=»101″;

elsif A=’0′ and B=’1′ then

D<=»110″;

elsif A=’1′ and B=’1′ then

D<=»111″;

elsif S1=’0′ and (A=’1′) or

(A=’0′) and B=’1′ then

D<=»111″;

end if;

end process;

end k155id4;

Модель элемента К155ЛА2.

library IEEE;

use IEEE.std_logic_1164.all;

entity k155la2 is

port (

V: in

STD_LOGIC_VECTOR (0 to 4);

F:out STD_LOGIC

);

end k155la2;

architecture k155la2 of

k155la2 is

begin

process(V)

begin

F<=transport not(V(1)

and V(2) and V(3) and V(4) and V(0)) after 22 ns;

end process;

end k155la2;

Модель элемента К155ЛА3.

library IEEE;

use IEEE.std_logic_1164.all;

entity k155la3 is

port (

X1: in STD_LOGIC;

X2: in STD_LOGIC;

J: out STD_LOGIC

);

end k155la3;

architecture k155la3 of

k155la3 is

begin

process(X1,X2)

begin

J<=not(X1 and X2)

after 22 ns;

end process;

end k155la3;

Модель элемента КР580ИК51.

library IEEE;

use IEEE.std_logic_1164.all;

entity kp580ik51 is

port (

in1:inout

STD_LOGIC_VECTOR (0 to 7);

sbr: in STD_LOGIC;

UD: in STD_LOGIC;

rd: in STD_LOGIC;

wr: in STD_LOGIC;

out1: inout

STD_LOGIC;

gpd: inout STD_LOGIC;

gpr: inout

STD_LOGIC

);

end kp580ik51;

architecture kp580ik51 of

kp580ik51 is

begin

process

(in1,sbr,UD,rd,wr,gpd,gpr,out1)

variable i:integer;

begin

if (sbr=’0′)

and (UD=’0′) then

if (wr=’1′)

and (rd=’0′) then

for i in 7

downto 0 loop

out1<=transport

in1(i) after 23 ns;

end loop;

else

for

i in 7 downto 0 loop

in1(i)<=transport

out1 after 20 ns;

end

loop;

gpd<=’1′;

gpr<=’1′;

end if;

end if;

end process;

end kp580ik51;

Модель элемента К155ЛН5.

library IEEE;

use IEEE.std_logic_1164.all;

entity k155ln5 is

port (

H: in STD_LOGIC;

K: out STD_LOGIC

);

end k155ln5;

architecture k155ln5 of

k155ln5 is

begin

process(H)is

begin

K<=transport not H after

22 ns;

end process;

end k155ln5;

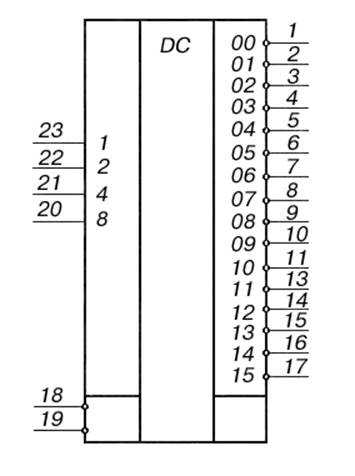

2.3 Дешифратор К155ИД3

К155ИД3 — дешифратор, позволяющий

преобразовать четырехразрядный код, поступающий на входы А0-А3 в напряжение

низкого логического уровня, появляющееся на одном из шестнадцати выходов 0-15.

Дешифратор имеет два входа разрешения дешифрации Е0 и Е1. Эти входы можно использовать

как логические, когда дешифратор ИД3 служит демультиплексором данных. Тогда

входы А0-А3, используются как адресные, чтобы направить поток данных,

принимаемых входами Е0 или Е1, на один из выходов 0-15. На второй, не

используемый в этом включении вход Е, следует подать напряжение низкого уровня

Схема электрическая

принципиальная приведена на рис.5.

Рис.5.

Схема электрическая принципиальная К155ИД3

По входам Е0 и Е1 даются сигналы разрешения выходов,

чтобы устранять текущие выбросы, которыми сопровождается дешифрация кодов,

появляющихся не строго синхронно (например, поступающих от счетчика пульсаций).

Чтобы разрешить прохождение данных на выходы, на входы Е0 и Е1 следует дать

напряжение низкого уровня. Эти входы необходимы также при наращивании числа

разрядов дешифрируемого кода. Когда на входах Е0 и Е1 присутствуют напряжения

высокого уровня, на выходах 0-15 появляются высокие уровни.

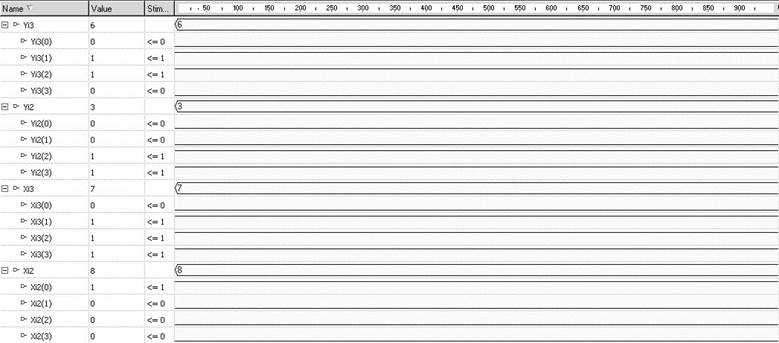

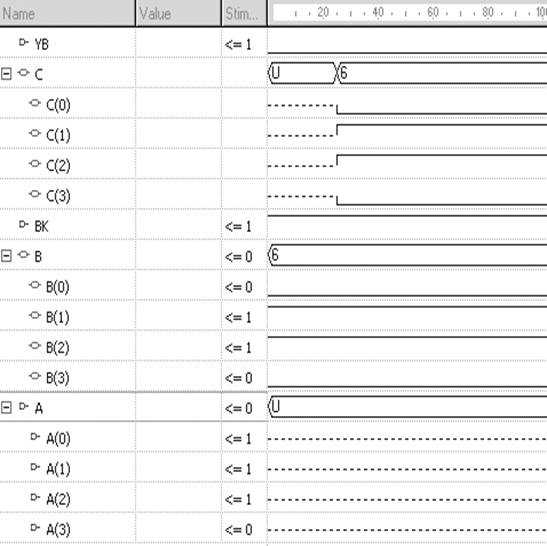

Рис.6. Временная

диаграмма работы дешифратора К155ИД3