4.5.Файл IC_k589ir12.vhd

——————————————————————-

— File: ..\SRC\IC_k155ir12.vhd

——————————————————————-

library IEEE;

use IEEE.std_logic_1164.all;

library SYNOPSYS;

use SYNOPSYS.std_logic_arith.all;

use SYNOPSYS.std_logic_unsigned.all;

entity IC_k589ir12 is

port

DAin: in STD_LOGIC_VECTOR(7 downto 0);

R: in STD_LOGIC;

BM1: in STD_LOGIC;

BM2: in STD_LOGIC;

CT: in STD_LOGIC;

BP: in STD_LOGIC;

QAout:out STD_LOGIC_VECTOR(7 downto

0):=»00000000″;

INR: out STD_LOGIC:=’0′

);

end IC_k589ir12;

architecture IC_k589ir12 of IC_k589ir12 is

signal Regist:STD_LOGIC_VECTOR(7 downto

0):=»00000000″;

begin

process(R, BM1, BM2, CT, BP)

begin

if R’event and R=’0’then

QAout <= «00000000»;

else

if (CT and not BM1 and BM2) =’1′ then

QAout <= transport DAin after 30 ns;

else

QAout <= transport «00000000» after

30 ns;

end if;

end if;

end process;

end IC_k589ir12;

4.6.Файл Top.vhd

——————————————————————-

— File: ..\SRC\Top.VHD

——————————————————————-

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_unsigned.all;

entity Top is

port

In1: inout STD_LOGIC;

In2: inout STD_LOGIC;

A0: in STD_LOGIC;

A1: in STD_LOGIC;

OBB: in STD_LOGIC;

Read: in STD_LOGIC;

Write: in STD_LOGIC;

At: out STD_LOGIC;

Ct: out STD_LOGIC;

Dt: out STD_LOGIC;

TPR: out STD_LOGIC;

D: out STD_LOGIC_VECTOR (11 downto 0)

);

end Top;

architecture Structure of Top is

component N_AND is

port

a: in STD_LOGIC;

b: in STD_LOGIC;

c: out STD_LOGIC

);

end component;

component k155ie5 is

port

CLK: in STD_LOGIC;

RESET: in STD_LOGIC;

Q: out STD_LOGIC_VECTOR (3 downto 0)

);

end component;

component k155tm2 is

port

Sin: in STD_LOGIC;

Din: in STD_LOGIC;

Cin: in STD_LOGIC;

Rin: in STD_LOGIC;

Q: inout STD_LOGIC;

Q_inv: out STD_LOGIC

);

end component;

component k589ir12 is

port

DAin: in STD_LOGIC_VECTOR(7 downto 0);

R: in STD_LOGIC;

BM1: in STD_LOGIC;

BM2: in STD_LOGIC;

CT: in STD_LOGIC;

BP: in STD_LOGIC;

QAout:out STD_LOGIC_VECTOR(7 downto 0);

INR: out STD_LOGIC

);

end component;

component k155id4 is

port

A0: in STD_LOGIC;

A1: in STD_LOGIC;

D1: in STD_LOGIC;

D2: in STD_LOGIC;

C1: in STD_LOGIC;

C2: in STD_LOGIC;

Q0: out STD_LOGIC_VECTOR (3 downto 0);

Q1: out STD_LOGIC_VECTOR (3 downto 0)

);

end component;

signal a_bus:STD_LOGIC_VECTOR (16 downto 1);

signal s1, s2, s3, s4, s5, s6, s7, s8, s9, s10,

s11, s12, s13, s14, s15:STD_LOGIC;

signal grn, one:STD_LOGIC;

signal s12_out, s18_Q0_out, s18_Q1_out:STD_LOGIC_VECTOR(3 downto

4.4.Файл IC_k155id4.vhd

——————————————————————-

— File: ..\SRC\IC_k155id4.vhd

——————————————————————-

library IEEE;

use IEEE.std_logic_1164.all;

library SYNOPSYS;

use SYNOPSYS.std_logic_arith.all;

use SYNOPSYS.std_logic_unsigned.all;

entity IC_k155id4 is

port

A0: in STD_LOGIC;

A1: in STD_LOGIC;

D1: in STD_LOGIC;

D2: in STD_LOGIC;

C1: in STD_LOGIC;

C2: in STD_LOGIC;

Q0: out STD_LOGIC_VECTOR (3 downto 0);

Q1: out STD_LOGIC_VECTOR (3 downto 0)

);

end IC_k155id4;

architecture IC_k155id4 of IC_k155id4 is

signal Qres0:STD_LOGIC_VECTOR (3 downto 0);

signal Qres1:STD_LOGIC_VECTOR (3 downto 0);

begin

Qres0 <=

«0111» when (A0 & A1 & D2 &

D1)=»0001″ else

«1011» when (A0 & A1 & D2 &

D1)=»0101″ else

«1101» when (A0 & A1 & D2 &

D1)=»1001″ else

«1110» when (A0 & A1 & D2 &

D1)=»1101″ else

«1111»;

Qres1 <=

«0111» when (A0 & A1 & C1 &

C2)=»0011″ else

«1011» when (A0 & A1 & C1 &

C2)=»0111″ else

«1101» when (A0 & A1 & C1 &

C2)=»1011″ else

«1110» when (A0 & A1 & C1 &

C2)=»1111″ else

«1111»;

Q0 <= transport Qres0 after 32 ns;

Q1 <= transport Qres1 after 32 ns;

end IC_k155id4;

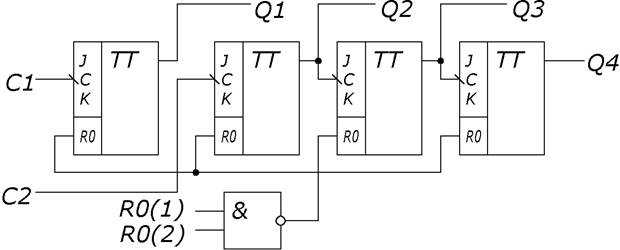

3.2. Микросхема К155ИЕ5

Микросхема представляет собой четырехразрядный

двоичный асинхронный счетчик.

Микросхема счетчика состоит из четырёх JK-триггеров,

которые соединены

соответствующим образом (Рис.5) для образования счетчика

делителя на 2 и 8.

Рис.4. Условное графическое обозначение

К155ИЕ5

Рис.5. Функциональная схема К155ИЕ5

Назначение выводов

|

Вывод |

Назначение |

Вывод |

Назначение |

|

|

1 |

Вход счетный С2 |

8 |

Выход Q3 |

|

|

2 |

Вход установки в 0 R0(1) |

9 |

Выход Q2 |

|

|

3 |

Вход установки в 0 R0(2) |

10 |

Общий |

|

|

4 |

Свободный |

11 |

Выход Q4 |

|

|

5 |

Напряжение питания |

12 |

Выход Q1 |

|

|

6 |

Свободный |

13 |

Свободный |

|

|

7 |

Свободный |

14 |

Вход счетный С1 |

Время задержки распространения 135 нс.

У счетчика имеются лишь входы сброса в нуль. Счетчик

работает по заднему фронту положительного входного сигнала. Выделены две

части: один триггер (одноразрядный счетчик) со входом С1 и выходом 1 и три

триггера (трехразрядный счетчик) со входом С2 и выходами 2, 4, 8. Оба

счетчика двоичные, то есть первый считает до двух, а второй — до 8. При

объединении входа С2 с выходом 1 получается 4-разрядный двоичный счетчик,

считающий до 16. Счет производится по отрицательному фронту входного сигнала.

Предусмотрена возможность сброса в нуль по сигналам R1 и R2, объединенных

функцией И.

Таблица истинности счетчика ИЕ5 присоединении входа С2 и

выхода 1 (при 4-разрядном выходном коде):

|

Входы |

Выходы |

|||||

|

С1 |

R1 |

R2 |

8 |

4 |

2 |

1 |

|

Х |

1 |

1 |

||||

|

1→0 |

Х |

Счет |

||||

|

1→0 |

Х |

Счет |

Счет производится согласно следующей

таблице:

|

Счет |

Выход |

|||

|

8 |

4 |

2 |

1 |

|

|

1 |

1 |

|||

|

2 |

1 |

|||

|

3 |

1 |

1 |

||

|

4 |

1 |

|||

|

5 |

1 |

1 |

||

|

6 |

1 |

1 |

||

|

7 |

1 |

1 |

1 |

|

|

8 |

1 |

|||

|

9 |

1 |

1 |

||

|

10 |

1 |

1 |

||

|

11 |

1 |

1 |

1 |

|

|

12 |

1 |

1 |

||

|

13 |

1 |

1 |

1 |

|

|

14 |

1 |

1 |

1 |

|

|

15 |

1 |

1 |

1 |

1 |

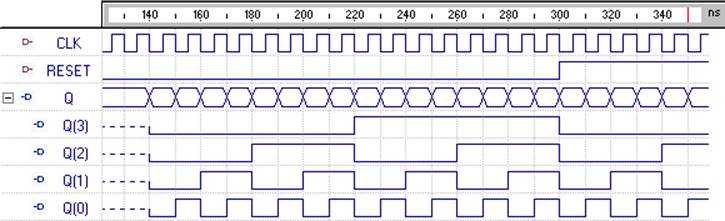

Рис.6. WaveForm К155ИЕ5

4.3.Файл IC_k155tm2.VHD

——————————————————————-

— File: ..\SRC\IC_k155tm2.VHD

——————————————————————-

library IEEE;

use IEEE.std_logic_1164.all;

library SYNOPSYS;

use SYNOPSYS.std_logic_arith.all;

use SYNOPSYS.std_logic_unsigned.all;

entity IC_k155tm2 is

port

Sin: in STD_LOGIC;

Din: in STD_LOGIC;

Cin: in STD_LOGIC;

Rin: in STD_LOGIC;

Q: inout STD_LOGIC;

Q_inv: out STD_LOGIC

);

end IC_k155tm2;

architecture IC_k155tm2 of IC_k155tm2 is

signal Qt:STD_LOGIC;

begin

process (Rin, Sin, Cin)

begin

Qt<= Q;

if (Rin=’0′ and Sin=’1′) then Qt <=

‘0’;

elsif (Rin=’1′ and Sin=’0′) then Qt <=

‘1’;

elsif (Rin=’1′ and Sin=’1′) then

if(Cin’event and Cin=’1′) then

if(Din=’1′)

then Qt <= ‘1’;

else Qt <= ‘0’;

end if;

end if;

else

assert not (Sin=’0′ and Rin=’0′)

report «одновременный 0 на S и R входе

D-триггера»

severity warning;

end if;

Q <= transport Qt after 40 ns;

Q_inv <= transport not Qt after 40 ns;

end process;

end IC_k155tm2;

4.2.Файл IC_k155ie5.vhd

——————————————————————-

— File: ..\SRC\IC_k155ie5.vhd

——————————————————————-

library IEEE;

use IEEE.std_logic_1164.all;

library SYNOPSYS;

use SYNOPSYS.std_logic_arith.all;

use SYNOPSYS.std_logic_unsigned.all;

entity IC_k155ie5 is

port

CLK: in STD_LOGIC;

RESET: in STD_LOGIC;

Q: out STD_LOGIC_VECTOR (3 downto 0)

);

end IC_k155ie5;

architecture IC_k155ie5 of IC_k155ie5 is

begin

process (CLK, RESET)

variable Qint: STD_LOGIC_VECTOR (3 downto 0);

begin

if RESET=’1′ then

Qint := «0000»;

else

if CLK’event and CLK=’1′ then

if Qint<15 then

Qint:=Qint+1;

else

Qint:=»0000″;

end if;

end if;

end if;

Q <= transport Qint after 135 ns;

end process;

end IC_k155ie5;

Потенциометры

Потенциометры, содержащие драгметаллы.

- ППМЛ-М, ППМЛ-И, ППМЛ-ИМ, ППМЛ-Ф, ППМФ-М, ППБЛ-В, РПП, ПТП-1, ПТП-2, ПТП-5, ПЛП-1, ПЛП-2.

- Некоторые потенциометры не подходят для продажи, так как внутри проволока встречается из нихрома или манганина.

Реле отечественного и импортного производства, содержащие драгметаллы.

- РЭС7, РЭС8, РЭС9, РЭС10, РЭС14, РЭС15, РЭС22, РЭС32, РЭС34, РЭС37, РЭС48, РЭС78.

- РП3, РП4, РП5, РП7, РПС3, РПС4, РПС5, РПС7, РПС11, РПС15, РПС18, РПС20, РПС24, РПС32, РПС34, РПС36.

- ДП12, РКН, РКНМ, РКМ-1, РКМ-1Т, РКМ-П, РЭК43, РЭН-33, ТРА, ТРВ, ТРЛ, ТРМ, ТРН, ТРП, ТРТ, РТН, ТРСМ-1, ТРСМ-2, РВМУ-1, РКП Е-506, СК-594, РВ-5А, РТС-5.

- Перечисленные реле подходят не все, а только с определёнными паспортами и до определённого месяца и года выпуска.

- Реле РЭС-6, РЭС-22, РЭС-32 с белыми контактами в целом виде не подходят для продажи, снимайте алюминиевый корпус (крышку) и проверяйте цвет контактов. Если белые, то делайте срезку контактов.

- Реле РЭС-22, РЭС-32 в целом виде покупаем только с жёлтыми контактами. Срезку контактов не надо делать, присылайте или привозите реле с целыми корпусами, так как на корпусе находится маркировка. А это, в свою очередь, напрямую влияет на цену реле.

- Реле РЭС-9 с паспортами 00 01 и 200 стоят 2 рубля/ед..

- У реле РЭС-10 при демонтаже должны быть сохранены внешние выводы (ноги). Без выводов данное реле существенно дешевле.

- Реле РЭС-47, РЭС-49, РЭС-60 в целом виде покупаем на вес, отправлять Почтой России не особо рентабельно. Возможно разобрать данные реле на жёлтые контакты-пластинки и в таком виде отправлять. Цена в этом случае будет высокой.