Регистры и счётчики

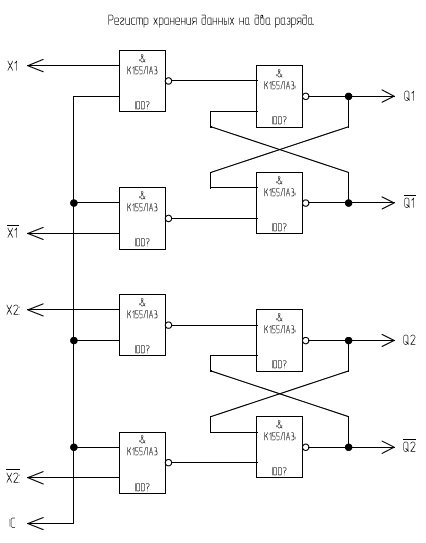

Дешевизна (в смысле меньшего количества необходимых логических элементов) RS-триггеров по сравнению с триггерами других типов побуждала конструкторов как можно более широко использовать именно их. Типичный регистр, принимающий данные с некоторой шины, в собранных на «рассыпухе» машинах состоит не из «современных» D-триггеров, принимающих информацию со входа D по фронту синхросигнала (общепринятое русское название для них так и не придумали, обычно называя просто D-триггерами, а сейчас нередко используют английское — flip-flop; такие триггеры, конечно, не являются современным изобретением — в 1960-х они уже точно встречались, но довольно редко в силу своей относительной сложности) и даже не из защёлок, а из «честных» тактируемых RS-триггеров.

«Секрет» заключается в том, что в ранних машинах информация по шинам очень часто передавалась с использованием так называемых парафазных сигналов, внешне напоминающих современные дифференциальные пары: если по одному проводу передаётся высокий уровень, то по второму — низкий, и наоборот. Сходство, однако, чисто внешнее: если логическое значение дифференциального сигнала (1 или 0) определяется разностью напряжений на передающих его линиях, а напряжения каждой из линий пары сами по себе безразличны (в разумных пределах, конечно), то в случае парафазного сигнала обе образующих его линии технически являются совершенно независимыми сигналами с обычными логическими уровнями, просто один из них всегда инвертирован по отношению к другому. Благодаря этому парафазные сигналы могут напрямую управлять RS-триггерами, а их формирование, как правило, не требует дополнительных аппаратных затрат: на вход одного регистра зачастую поступает информация с выхода другого регистра, а соответственно, прямое и инверсное значения каждого бита уже имеются.

Дополнительным бонусом от использования парафазных сигналов являются расширенные возможности контроля правильности передачи информации: если на момент приёма данных обе линии парафазного сигнала имеют одинаковое значение, значит, что-то где-то сломалось. Впрочем, организация аппаратного контроля работы машины — отдельная тема.

Довольно остроумно решается и проблема приёма и хранения данных, считываемых из памяти, с минимальными затратами оборудования. Регистр данных тоже строится на RS-триггерах, причём на сей раз самых простых — даже без входа тактирования. В начале цикла считывания все триггеры регистра сбрасываются в нуль (сигналом сброса в данном случае может служить сигнал занесения адреса в регистр адреса памяти, с чего начинается обращение к ней). Считывание единичного бита из некоторого разряда ячейки памяти вызывает появление импульса на входе усилителя считывания, который усиливает его и при необходимости растягивает во времени, после чего передаёт на вход установки соответствующего триггера регистра данных. Как следствие, триггеры регистра данных для тех разрядов ячейки памяти, которые хранили единицы, устанавливаются, а остальные триггеры остаются сброшенными.

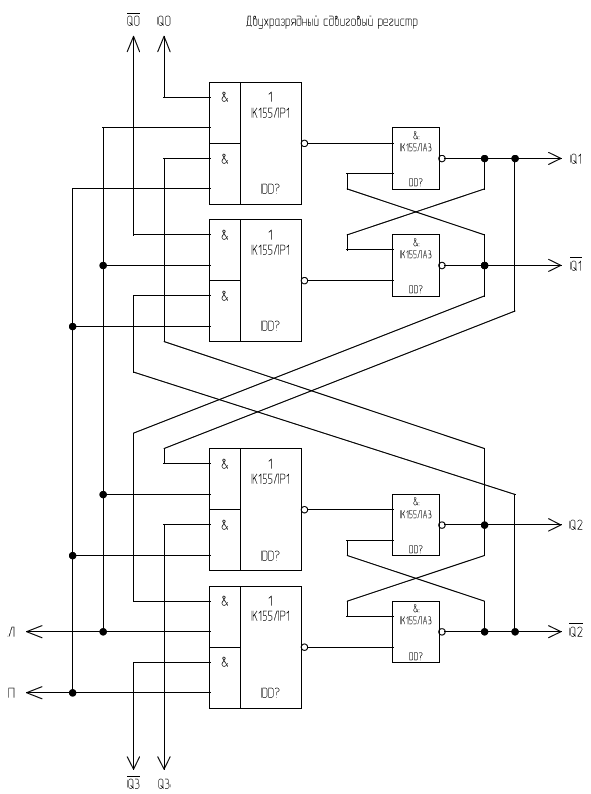

Сдвиговый регистр тоже собирается на слегка модифицированных RS-триггерах. Как видно на схеме, первый каскад образован элементами 2,2И-2ИЛИ-НЕ, на каждый из входных элементов И которых подаётся свой управляющий сигнал П или Л, вызывающий соответственно сдвиг вправо или влево. Кстати, насчёт обозначений П и Л: в документации на ранние машины действительно используется русско-английская смесь, где П и Л соседствуют с R и D — благо, ватманы с кульманами, в отличие от многих САПР, всё стерпят.

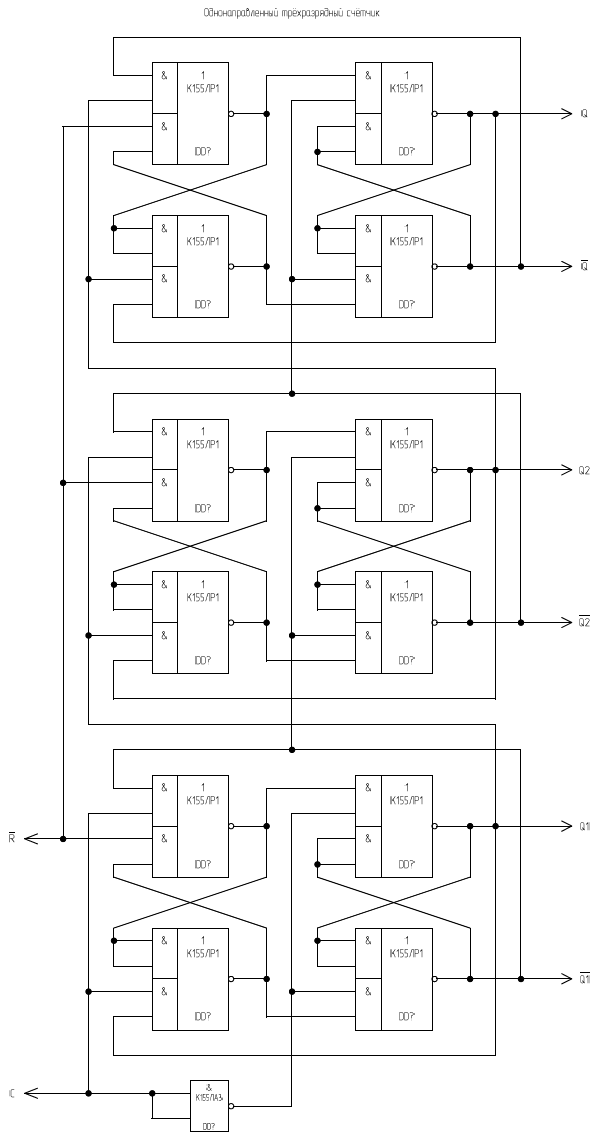

Счётчики создаются на основе счётных триггеров. В качестве примера показана схема 3-разрядного однонаправленного счётчика со входом сброса на основе элементов 2,2И-2ИЛИ-НЕ. Каждый его разряд требует две микросхемы ЛР1; кроме того, требуется ещё один инвертор на весь счётчик.

Комбинационные схемы

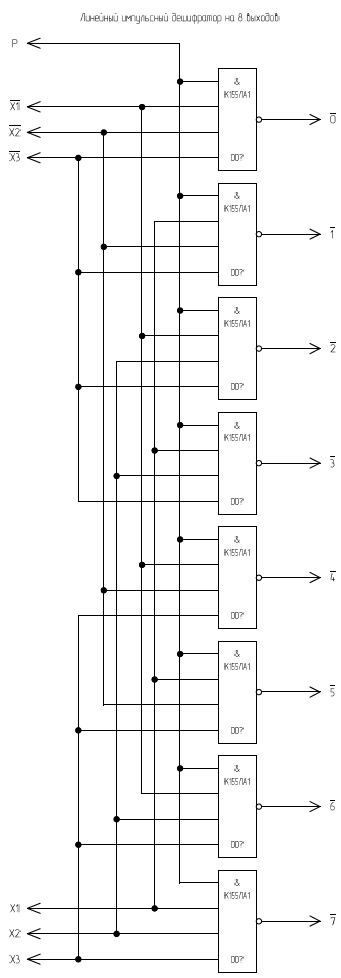

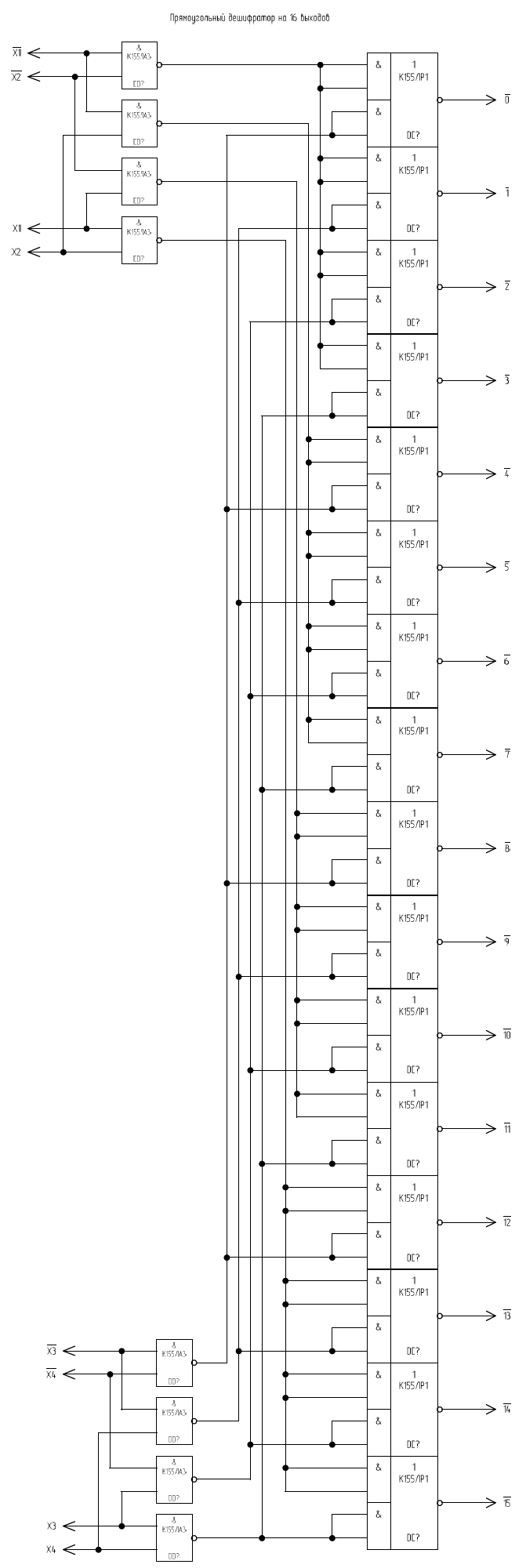

Вполне ожидаемо, что «ископаемые» дешифраторы по своему устройству, по большому счёту, не отличаются от более современных. Единственным заметным отличием является то, что в состав «рассыпных» схем обычно не включаются инверторы, необходимые для формирования обратных значений исходных сигналов: поскольку почти всегда входная информация подаётся с регистров, а те выполнены на триггерах, имеющих и прямой, и инверсный выходы, совершенно естественно пользоваться их «услугами». В качестве примера показаны схемы так называемых линейного импульсного дешифратора на 8 выходов («импульсный» в данном случае означает наличие дополнительного входа управления, разрешающего или запрещающего работу дешифратора, благодаря чему на одной из выходных линий можно в нужный момент времени сформировать импульс) и прямоугольного дешифратора на 16 выходов. Как видим, выходы у них всегда инвертированные; если нужно получить результат в прямом виде, приходится ставить инверторы.

Мультиплексоры в явном виде как отдельные законченные функциональные блоки в конструкции ранних машин не выделялись, хотя они, конечно, были. Собственно выбор одного из входных сигналов и передача его на выход осуществляется элементом И-ИЛИ-НЕ на нужное число входов (два у ЛР1 и четыре у ЛР3, при необходимости они дополняются расширителями ЛД1). Какой именно из элементов И будет открыт, определяется управляющими сигналами, поступающими с дешифратора, а последний в типичном случае управляется выходами некоего регистра. Таким образом, мультиплексор в современном понимании оказывается «размазан» между: 1) выходами регистра, содержащего код источника (оттуда поступают прямые и инверсные значения разрядов кода), 2) дешифратором кода источника, 3) инверторами на выходах дешифратора (поскольку с него поступают инвертированные сигналы, а управлять они должны элементами И — т. е. быть прямыми) и 4) схемой выбора одного из входных сигналов на элементах И-ИЛИ-НЕ.

Вот устройство самой сложной комбинационной схемы ранних машин — АЛУ — заметно отличается от, например, классической микросхемы К155ИП3, в девичестве SN74181. Впрочем, эта тема весьма обширна и заслуживает отдельной статьи.

Литература

-

В. В. Пржиялковский и др. Электронная вычислительная машина ЕС-1020. Под общей редакцией А. М. Ларионова. — М., «Статистика», 1975

-

Р. М. Асцатуров и др. Процессор ЭВМ ЕС-1020. Под общей редакцией А. М. Ларионова. — М., «Статистика», 1975

-

Р. И. Абражевич и др. Каналы ввода-вывода ЭВМ ЕС-1020. Под общей редакцией А. М. Ларионова. — М., «Статистика», 1975

-

А. Т. Кучукян и др. Электронная вычислительная машина ЕС-1030. Под общей редакцией А. М. Ларионова. — М., «Статистика», 1977

(К)1ЛБ331(Б)

|

Два логических элемента 4И-НЕ. Первые Справочный листок и |

Что касается буквы «Б» — то, как пишет Погорилый «…некоторое

время 133 серия выпускалась с буквенными индексами А и Б (1ЛБ333А и 1ЛБ333Б, например). У «А»

было быстродействие больше, у «Б» несколько меньше.

Микросхемы с пониженной нагрузочной способностью и пониженным быстродействием

(25 и 50 нс вместо 15 и 22), т.е. «полубрак по параметрам», выпускала и фирма TI в начальный

период производства серии 54/74. Так что это обычная ситуация на этапе освоения

производства, пока технология еще не отработана».

Судя по фото, в них могли стоять разные кристаллы! По крайней мере,

если смотреть на расположение контактных площадок на интеграловских кристаллах:

|

образец 1972 года: |

образец 1976 года: |

К1ЛП332

Интереснейший экземпляр!

Во-первых, этой микросхемы нет практически ни в одном справочнике.

1ЛП331 есть, 1ЛП333 есть, а вторая пропущена!

Это были «половинки»; 1ЛП332 — половина 133ЛД1 (1ЛП331), один 4-входовый расширитель по ИЛИ.

Очень скоро производство их было прекращено, т.к. стало получаться достаточно нормальных, не половинок.

Память от них осталась в виде «дырок» в порядке номеров типов микросхем.

В-третьих, корпус. Видны рудиментарные боковые выводы. Назначение

неизвестно, то ли пытались втиснуть дополнительные выводы, то ли для крепления к рамке при изготовлении.

Плюс к этому, очень острые грани корпуса, такого тоже не встречал более.

Мало? Могу добавить и в-четвертых :))). Это (пока) самая ранняя микросхема из

этой серии у меня. Выпуск менее чем через год после окончания разработки…